# Reference System: OPB IIC Using the ML403 Evaluation Platform

Author: Paul Glover, Ed Meinelt, Lester Sanders

# Summary

This application note describes how to build a reference system for the On-Chip Peripheral Bus Inter IC (OPB IIC) core using the IBM PowerPC<sup>™</sup> 405 Processor (PPC405) based embedded system in the ML403 Embedded Development Platform. The reference system is Base System Builder (BSB) based.

An IIC primer is given and an OPB IIC register reference is provided. The Xilinx Microprocessor Debugger (XMD) commands are used for verifying that the OPB IIC core operates correctly. Several software projects illustrate how to configure the OPB IIC core, set up interrupts, and do read and write operations. Some of the software projects interface the OPB IIC to the MicroChip 24LC04B serial EEPROM with an IIC interface, while others interface to the TotalPhase Aardvark Adapter, which provides IIC master and slave functionality. The procedure for using ChipScope<sup>™</sup> to analyze OPB IIC functionality is provided. The steps used to build a Linux kernel using MontaVista are listed. Simulation output files for analyzing basic IIC transactions are provided.

# Included Systems

This application note includes one reference system:

www.xilinx.com/bvdocs/appnotes/xapp979.zip

The project name used in xapp979.zip is ml403\_ppc\_opb\_iic.

# Required Hardware/Tools

Users must have the following tools, cables, peripherals, and licenses available and installed:

- Xilinx EDK 8.2.02i

- Xilinx ISE 8.2.03

- Xilinx Download Cable (Platform Cable USB or Parallel Cable IV)

- Monta Vista Linux v2.4 Development Kit

- Modeltech ModelSim v6.1d

- ChipScope v8.2

© 2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. PowerPC is a trademark of IBM Inc. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice. NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

# Introduction

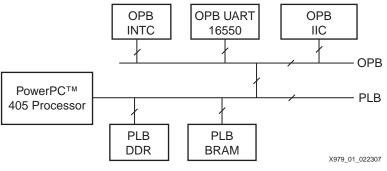

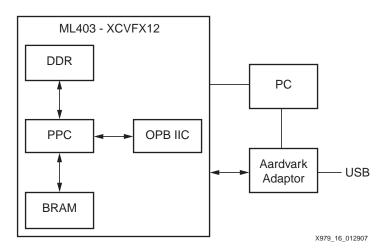

This application note accompanies a reference system built on the ML403 development board. Figure 1 is a block diagram of the reference system.

Figure 1: OPB IIC Reference System Block Diagram

The system uses the embedded PowerPC (PPC) as the microprocessor and the OPB IIC core.

### **IIC Primer**

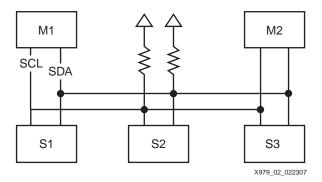

Figure 2 shows components on an IIC bus. Two IIC masters and three IIC slaves are shown. The master is responsible for setting up transactions. This includes generating the clock on SCL and defining which slave is involved in the communication, with an address field, and which component is transmitting and which component is receiving. Some components are slave only, while others can transition between master and slave operation.

Figure 2: IIC Bus

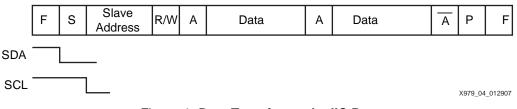

Figure 3 shows the START and STOP conditions. A START condition is a falling edge on SDA when SCL is high. A STOP condition is a rising edge on SDA when SCL is high. During data transfer, the data line is stable on SDA when SCL is high. Data transitions on SDA when SCL is low. Note that the START and STOP conditions are special conditions, violating the rule that data cannot transition while SCL is high.

Figure 3: Start and Stop Conditions

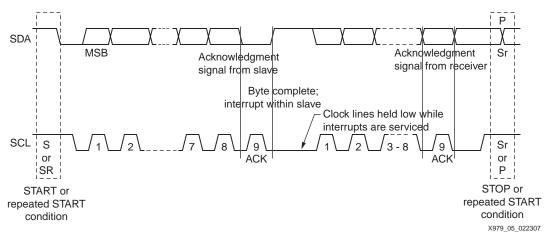

Figure 4 shows the format of the data transfer of two bytes on the IIC bus, beginning with the START (S) condition and ending with the STOP (P) condition, bounded by an idle IIC (F) bus. After a START condition, an eight bit field is transmitted containing a 7 bit address and a single Read/Write (R/W) bit. This 8 bit address/direction field is followed by an Acknowledge bit. After the address/data field, an eight bit data field is followed by an acknowledge bit (A). The last 8-bit data field is followed by a not acknowledge bit ( $\overline{A}$ ). This is followed by the STOP condition (P).

A single message can contain multiple start conditions, or a repeated start, without intervening STOP conditions.

In this data transfer, there are two acknowledge bits and one Not Acknowledge on the IIC bus. The distinction between a Not Acknowledge and a No Acknowledge is that Not Acknowledge occurs after a master has read a byte from a slave and a No Acknowledge occurs after a master has written a byte to a slave.

A synchronized SCL is generated with its LOW period determined by the device with the longest low period and its HIGH period determined by the device with the shortest HIGH period.

Figure 4: Data Transfer on the IIC Bus

Figure 5 shows the data transfer on the IIC bus, beginning with the START condition and ending with the STOP condition.

Figure 5: Generic Data Transer on the IIC Bus

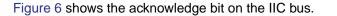

Figure 6: Acknowledge on the IIC Bus

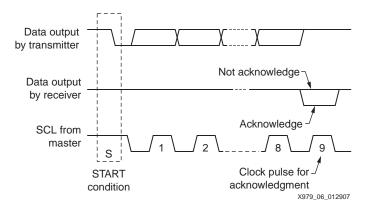

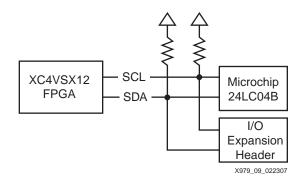

Figure 7 shows bus arbitration of two masters. The IIC bus is a multi-master bus. Masters monitor the IIC bus to determine if the bus is active. The bus is inactive when SCL and SDA are high for a bus free period tBUF of 1.3 us (FAST) or 4.7 us (STD). If two or more masters monitoring the IIC bus determine that the bus is free and begin a bus transaction simultaneously, the IIC bus is arbitrated to determine which master owns the bus. The IIC is a wired AND bus. This means that the bus is HIGH unless any component is driving it LOW.

Masters monitor the bus even after they have started a transaction as the master. If a master is not driving the IIC bus low and the bus is low, the master knows that another master is driving the IIC bus. If a master cannot get the SDA or SCL to go high it loses arbitration. When a master loses arbitration, it stops transmission. The master driving the bus with the last low when the other master(s) drives high becomes the master of the bus.

Figure 7: Arbitration of two Masters

# Reference System Specifics

In addition to the PowerPC405 processor and OPB IIC, this system includes DDR and BRAM memory on the PLB, and a UART and interrupt controller on the OPB. Figure 1 provides the block diagram. Table 1 provides the address map of the ML403 XC4VFX12. This is in the system.mhs.

### ML403 XC4VFX12 Address Map

Table 1: ML403 XC4VSX12 System Address Map

| Peripheral    | Instance            | Base Address | High Address |

|---------------|---------------------|--------------|--------------|

| PLB_DDR       | DDR_SDRAM_32Mx64    | 0x00000000   | 0x03FFFFFF   |

| OPB UART16550 | RS232_Uart_1        | 0x40400000   | 0x4040FFFF   |

| OPB INTC      | opb_intc_0          | 0x41200000   | 0x4120FFFF   |

| PLB BRAM      | plb_bram_if_cntlr_0 | 0xFFFF8000   | 0xffffffff   |

| OPB IIC       | IIC_EEPROM          | 0x40800000   | 0x4080FFFF   |

### **OPB IIC Registers**

Table 2 provides the register map for the OPB IIC core.

### Table 2: OPB IIC Registers

| Register                                           | Address            |

|----------------------------------------------------|--------------------|

| Device Global Interrupt Enable                     | C_BASEADDR + 0x01C |

| Interrupt Status Register                          | C_BASEADDR + 0x020 |

| Interrupt Enable Register                          | C_BASEADDR + 0x028 |

| Software Reset Register                            | C_BASEADDR + 0x040 |

| Control Register                                   | C_BASEADDR + 0x100 |

| Status Register                                    | C_BASEADDR + 0x104 |

| Transmit FIFO                                      | C_BASEADDR + 0x108 |

| Receive FIFO                                       | C_BASEADDR + 0x10C |

| Slave Address Register                             | C_BASEADDR + 0x110 |

| Transmit FIFO Occupancy                            | C_BASEADDR + 0x114 |

| Receive FIFO Occupancy                             | C_BASEADDR + 0x118 |

| Ten Bit Slave Address Register                     | C_BASEADDR + 0x11C |

| Receive FIFO Programmable Depth Interrupt Register | C_BASEADDR + 0x120 |

| General Purpose Output                             | C_BASEADDR + 0x124 |

Table 3 provides a description of the OPB IIC control register.

### Table 3: OPB IIC Control Register

| Bit(s) | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0- 24  | Reserved | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 25     | GC_EN    | <b>General Call Enable.</b> Setting this bit High allows the OPB IIC to respond to a general call address.                                                                                                                                                                                                                                                                                                      |

| 26     | RSTA     | <b>Repeated Start.</b> Writing a "1" to this bit generates a repeated START condition on the bus if the OPB IIC Bus Interface is the current bus Master. Attempting a repeated START at the wrong time, if the bus is owned by another Master, results in a loss of arbitration. This bit is reset when the repeated start occurs. This bit must be set prior to writing the new address to the Tx FIFO or DTR. |

| Bit(s) | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27     | ТХАК             | <b>Transmit Acknowledge Enable.</b> This bit specifies the value driven onto the SDA line during acknowledge cycles for both Master and Slave receivers. Because Master receivers indicate the end of data reception by not acknowledging the last byte of the transfer, this bit is used to end a Master receiver transfer. As a slave, this bit must be set prior to receiving the byte to no acknowledge. |

| 28     | ТХ               | <b>Transmit/Receive Mode Select.</b> This bit selects the direction of Master/Slave transfers. This bit does not control the Read/Write bit that is sent on the bus with the address. The Read/Write bit that is sent with an address must be the LSB of the address written into the transmit FIFO.                                                                                                         |

| 29     | MSMS             | <b>Master/Slave Mode Select.</b> When this bit is changed from 0 to 1, the OPB IIC Bus Interface generates a START condition in Master mode. When this bit is cleared, a STOP condition is generated and the OPB IIC Bus Interface switches to Slave mode. When this bit is cleared by the hardware, because arbitration for the bus has been lost, a STOP condition is not generated.                       |

| 30     | Tx FIFO<br>Reset | Transmit FIFO Reset. This bit must be set if arbitration is lost or if a transmit error occurs to flush the FIFO.                                                                                                                                                                                                                                                                                            |

| 31     | EN               | OPB IIC Enable. This bit must be set before any other CR bits have any effect                                                                                                                                                                                                                                                                                                                                |

### Table 3: OPB IIC Control Register (Contd)

### Status Register (SR)

This register contains the status of the OPB IIC Bus Interface. All bits are cleared upon reset. Table 4 provides a definition of the status register.

Table 4: Status Register Bit Definitions

| Bit(s) | Name              | Description                                                                                                                                                                                                                                                                                                                                                         |

|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 - 23 | N/A               | Reserved.                                                                                                                                                                                                                                                                                                                                                           |

| 24     | Tx_FIFO_<br>Empty | <b>Transmit FIFO empty.</b> This bit is set High when the transmit FIFO is empty.                                                                                                                                                                                                                                                                                   |

| 25     | Rc_FIFO_<br>Empty | <b>Receive FIFO empty.</b> This is set High when the receive FIFO is empty.                                                                                                                                                                                                                                                                                         |

| 26     | Rc_FIFO_<br>Full  | <b>Receive FIFO full.</b> This bit is set High when the receive FIFO is full.<br>This bit is set only when all sixteen locations in the FIFO are full, regardless of the value written into Rc_FIFO_PIRQ.                                                                                                                                                           |

| 27     | Tx_FIFO_F<br>ull  | Transmit FIFO full. This bit is set High when the transmit FIFO is full.                                                                                                                                                                                                                                                                                            |

| 28     | SRW               | <b>Slave Read/Write.</b> When the IIC Bus Interface has been addressed as a Slave (AAS is set), this bit indicates the value of the read/write bit sent by the Master. This bit is only valid when a complete transfer has occurred and no other transfers have been initiated. A "1" indicates Master reading from Slave. A "0" indicates Master writing to Slave. |

| 29     | BB                | <b>Bus Busy.</b> This bit indicates the status of the IIC bus. This bit is set when a START condition is detected and cleared when a STOP condition is detected.                                                                                                                                                                                                    |

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30     | AAS  | Addressed as Slave. When the address on the IIC bus matches the Slave address in the Address Register (ADR), the IIC Bus Interface is being addressed as a Slave and switches to Slave mode. If 10-bit addressing is selected this device will only respond to a 10-bit address or general call if enabled. This bit is cleared when a stop condition is detected or a repeated start occurs. |

| 31     | ABGC | Addressed By a General Call. This bit is set high when another master has issued a general call and the general call enable bit is set high, $CR(1) = '1'$ .                                                                                                                                                                                                                                  |

### Table 4: Status Register Bit Definitions (Contd)

Table 5 provides a register description of the Interrupt Status register.

### Table 5: Interrupt Status Register

| Bit | Name   | Description                            |

|-----|--------|----------------------------------------|

| 24  | TFHE   | Transmit FIFO Half Empty               |

| 25  | NAAS   | Not Addressed as Slave                 |

| 26  | AAS    | Addressed as Slave                     |

| 27  | BNB    | Bus is not Busy                        |

| 28  | RFF    | Receive FiFO Full                      |

| 29  | TFE    | Transmit FIFO Empty                    |

| 30  | TE/STC | Transmit Error/Slave Transmit Complete |

| 31  | AL     | Arbitration Lost                       |

### Configuring the OPB IIC Core

Figure 8 shows how to specify the values of IIC generics in EDK. To access the dialog box in the figure, double click on the OPB IIC core in the EDK System Assembly View.

|             |        | δ To                                  | HDL<br>ggle Names Datasheet | Restore |

|-------------|--------|---------------------------------------|-----------------------------|---------|

| User        | System |                                       |                             |         |

| 4 <u>  </u> |        | OPB Clock Frequency                   | 10000000                    | \$      |

|             |        | Output Frequency of SCL Signal        | 100000                      |         |

|             |        | Use 10-bit Address                    | 7-bit addresses             | *       |

|             |        | Width of GPI0                         | 1                           | *       |

|             |        | Device Block ID                       | 0                           | * >     |

|             |        | Enable Module Identification Register | 0                           | ٢       |

|             |        |                                       |                             | _       |

|             |        |                                       |                             |         |

|             |        |                                       |                             |         |

Figure 8: Specifying the Values of OPB IIC Generics in EDK

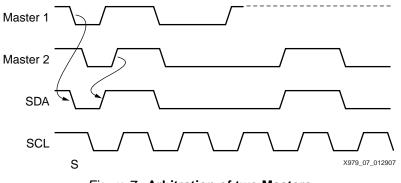

### Microchip 24LC04

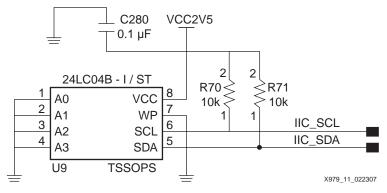

The Microchip Technology 24LC04B-I/ST with 4-KB EEPROM is provided on the ML403 board to store non-volatile data. The EEPROM write protect is tied off on the board to disable its hardware write protect. The IIC bus is extended to the expansion connector to allow additional devices to be added to the IIC bus.

Figure 9 shows IIC Bus Devices on the ML403.

Figure 9: ML403 IIC Bus

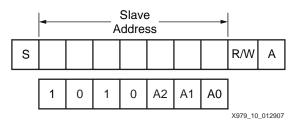

The 24LC04 is organized as two blocks of 256 bytes. It has a page write buffer of up to 16 bytes. The 24LC04 operates as an IIC slave. The 24LC04 accepts a control byte which contains control code, block select, and Read/Write fields shown in Figure 10. The control code

is '1010 for read and write operations. The A2, A1 bits are dont cares. The A0 bit is used by the master device to select which of the two 256-word blocks of memory are accessed. The 24LC04 write transactions are either a byte write or a page write. The page write begins the same as the byte write but instead of generating a stop condition the master transmits up to 16 data bytes to the 24LC04B. The 24LC04 supports current address, random, and sequential read operations.

Figure 10: 24LC04 Control Byte Allocation

# ML403 Board Information

According to the MicroChip 24L024B data sheet, the ML403 board has a low-level output current (IOL) of 3.0 mA at a VCC of 2.5v. The ML403 boards are shipped in the configuration shown in Figure 11. The board must be modified for this design to work correctly. Replace the 10K Ohm R70 and R71resistors with 833 or 1K Ohm resistors. See Answer Record 24049 for additional information.

Figure 11: ML40x Schematic for IIC Connections

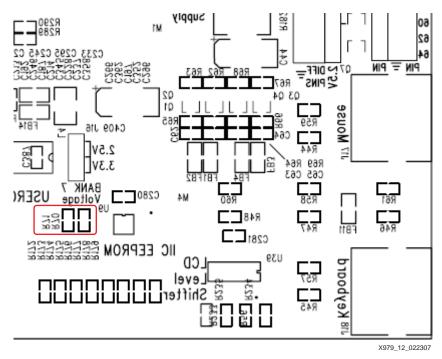

The resistors are located on the board as shown in Figure 12.

Figure 12: ML40x Resistors

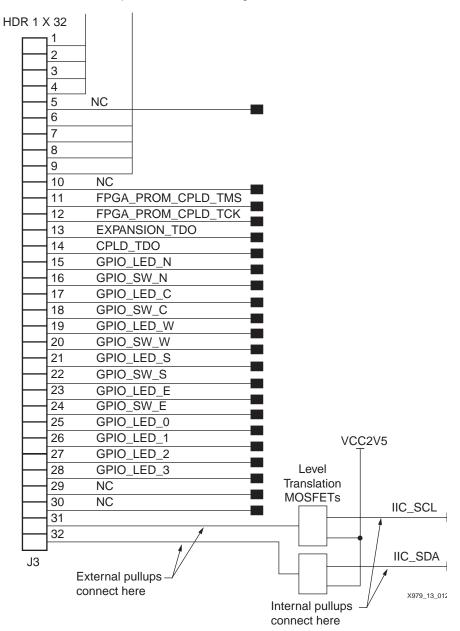

If additional IIC devices are connected to the bus via the expansion header as shown in Figure 13, insert additional pull-up resistors on the external signals connected at pins 31 and 32. The resistor values are dependent on the voltage.

Figure 13: Expansion Header

| IO_L8N_GC_LC_3_C12<br>IO_L8P_GC_LC_3_C13<br>IO_L7N_GC_LC_3_A17<br>IO_L7P_GC_LC_3_B17<br>IO_L6N_GC_LC_3_B10<br>IO_L6P_GC_LC_3_A10<br>IO_L5N_GC_LC_3_A15<br>IO_L5P_GC_LC_3_A16<br>IO_L4N_GC_VREF_LC_3_B12<br>IO_L4P_GC_LC_3_B13<br>IO_L3N_GC_LC_3_C14<br>IO_L3P_GC_LC_3_C15<br>IO_L2N_GC_VRP_LC_3_A11<br>IO_L2P_GC_VRN_LC_3_A12<br>IO_L1P_GC_CC_LC_3_B14 | C12<br>C13<br>A17<br>B17<br>B10<br>A10<br>A15<br>A16<br>B12<br>B13<br>C14<br>C15<br>A11<br>A12<br>B14 | SMA_DIFF_CLK_IN_N<br>SMA_DIFF_CLK_IN_P<br>IIC_SCL<br>IIC_SDA<br>DDR_CLK1_N<br>DDR_CLK1_P<br>DDR_A13<br>DDR_BA1<br>DDR_BA0<br>DDR_BA0<br>DDR_CLK_P<br>MOUSE_DATA<br>PHY_TXCLK<br>GPIO_LED_2<br>GPIO_LED_3<br>MOUSE_CLK |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_L1P_GC_CC_LC_3_B14<br>IO_L1P_GC_CC_LC_3_B15                                                                                                                                                                                                                                                                                                         | В14<br>B15                                                                                            | PHY_RXC_RXCLK                                                                                                                                                                                                         |

| FPGA_BANK3<br>2.5 VCC0                                                                                                                                                                                                                                                                                                                                 |                                                                                                       | X979 <u>1</u> 14_012907                                                                                                                                                                                               |

Figure 14 shows the FPGA pins driving the IIC Bus.

Figure 14: FPGA IIC Pins

### **TotalPhase Aardvark Adapter**

In the reference design, the OPB IIC in the XC4VFX12 on the ML403 board interfaces to the IIC in the Aardvark Adapter. The Aardvark IIC/SPI Embedded Systems interface is a multi-functional host adapter. The Aardvark Control Center software interacts with the Aardvark Adapter. The Control Center controls the functionality of the Aardvark Adapter. It uses the Aardvark IIC/SPI Software API. the Aardvark Adapter has six functional modes. The IIC-related modes are the IIC + SPI and IIC Bus Monitoring modes.

The Aardvark must be configured for use before the Aardvark Control Center software can be used to send and receive messages. Configuring the Aardvark Adapter binds the instance of the application with the available unit until the adapter is disconnected or the application is terminated.

The Configure Aardvark Adapter window is organized into two major sections: list of available adapters connected to the computer and list of the six operational modes. The main application window is divided into two sections. The top section contains the modules used with the Aardvark Adapter. The bottom section contains the transaction log which tracks all transactions that the Aardvark sends or receives. The transaction log contains the time, read or write transaction, master or slave, bit rate, address, number of bytes, and data.

| Figure | 15 | shows | the | Aardvark | Control | Center | GUI. |

|--------|----|-------|-----|----------|---------|--------|------|

|--------|----|-------|-----|----------|---------|--------|------|

| Aardvark 12C/SPI Control Center |                                                                                                                                                                                                                                                                                                     | I 🗆 🛛                  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| File Aardvark, Help             |                                                                                                                                                                                                                                                                                                     |                        |

|                                 | Configure Aardvark Adapter                                                                                                                                                                                                                                                                          |                        |

|                                 | Configure Aardvark Adapter         Select an Aardvark port           Select an Aardvark port         Select a Mode           P         FW         HW           12C         SPI         GPI           0         3.30         3.00         Y           Y         Y         2237-08507         SPI-GPI |                        |

| Transaction Log<br>Time Mod.    | C Batch Mode<br>C 12C Monitor<br>Refresh List<br>OK Cancel                                                                                                                                                                                                                                          |                        |

| Port Getting                    | g list of Aardvarks                                                                                                                                                                                                                                                                                 | Clear Log Save to File |

| denni<br>denni                  | INSU OF MATUYAINS                                                                                                                                                                                                                                                                                   | X979 15 01290          |

Figure 15: Aardvark Control Center

# Interfacing to the OPB IIC on the ML403 Board to the Aardvark Adapter

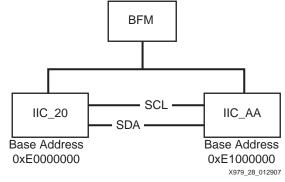

Figure 16 shows the principle interface blocks when transferring data between the OPB IIC in the XC4VFX12 on the ML403 board and the IIC in the Aardvark Adapter.

Figure 16: Interfacing ML403 Board OPB IIC with the Aardvark Adapter

# Executing the Reference System using the Pre-Built Bitstream and the Compiled Software Applications

To execute the system using files inside the ml403\_ppc\_opb\_IIC/ready\_for\_download directory, follow these steps:

- 1. Change to the ml403\_ppc\_opb\_IIC/ready\_for\_download directory.

- Use iMPACT to download the bitstream by using the following: impact -batch xapp.cmd

- 3. Invoke XMD and connect to the MicroBlaze processor by the following command: xmd -opt xapp.opt

- Download the executable by the following command dow <path>/executable.elf

### **Executing the Reference System from EDK**

To execute the system using EDK, follow these steps:

- 1. Open system.xmp inside EDK.

- 2. Use Hardware  $\rightarrow$  Generate Bitstream to generate a bitstream

- 3. Download the bitstream to the board using **Device Configuration**  $\rightarrow$  **Download Bitstream**.

- 4. Invoke XMD with Debug Launch XMD.

- Download the executable by the following command. dow <path>/executable.elf

### Verifying the Reference Design with Xilinx Microprocessor Debugger

After downloading the bitstream file, issue the following XMD commands to verify that the ML403 reference design is set up correctly.

mrd 0x42600100 8

The expected value of the control register after a reset, located at 0x42600100 is 0x00000000. The expected value of the status register, located at 0x42600104, is 0x000000C0. The reset values of the Transmit and Receive FIFO registers are indeterminate. The reset values of the Transmit and Receive FIFO Occupancy and the Address registers is 0.

Except for the Status, , Receive FIFO, and Transmit and Receive Occupancy registers, all registers are writeable.

mwr 0x42600100 0xFFFFFFF

mrd 0x42600100 1

Using XMD commands, verify that the OPB IIC registers can be written and read as defined in Tables 2-5.

### **Software Projects**

The reference system contains the following software projects. In each software project directory, there is a src sub-directory for the source code. The connections in Figure 9 are used for the eeprom, low\_level\_eeprom, dynamic\_eeprom, and low\_level\_dynamic\_eeprom projects. These projects interface to the 24LC04. The connections in Figure 3 are used for the mult\_master and repeated\_start project. These projects interface to the IIC Bus via the Aardvark Adapter.

### **Projects interfacing to Microchip 24LC04**

**eeprom**: This project transmits and receives data using the high level (L1) software driver. The OPB IIC is the master and the 24LC04 is configured as the slave. The OPB IIC master writes data into the 24LC04 and reads it back.

**low\_level\_eeprom**: This project transmits and receives data using the low level (L0) software driver. The OPB IIC is the master and the 24LC04 is configured as the slave. The OPB IIC master writes data into the 24LC04 and reads it back. This is a polled mode example.

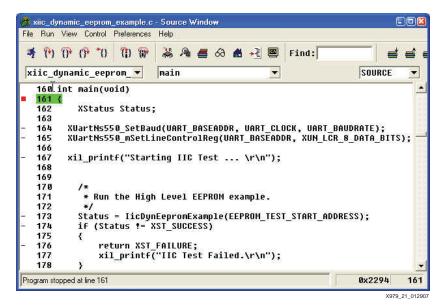

**dynamic\_eeprom**: This project transmits and receives data using the high level (L1) software driver. The OPB IIC is the master and the 24LC04 is configured as the slave. The OPB IIC master writes data into the 24LC04 and reads it back.

**low\_level\_dynamic\_eeprom**: This project transmits and receives data using the low level (L0) software driver. The OPB IIC is the master and the 24LC04 is configured as the slave. The OPB IIC master writes data into the 24LC04 and reads it back. This is a polled mode example.c

### **Projects interfacing to Aardvark Adapter**

**multi\_master**: This project transmits and receives data using the high level (L1) software driver. The OPB IIC is an IIC master and the IIC in the Aardvark is a master. The Microchip 24LC04B is configured as a IIC slave. The WP pin of the 24LC04 is hardwired to ground on the ML403. The interrupt mode is used. The IIC master in the Aardvark Adapter writes the data to the MicroChip 24LC04B with the No Stop option enabled. Any attempts to write data from the OPB IIC master results in a Bus Busy status. The Aardvark Adapter releases the bus by executing the FREE BUS command. When the bus is free, the OPB IIC master initiates a bus transaction.

**repeated\_start**: This project transmits and receives the data using the high level (L1) driver. The IIC devices on the ML300/ML310/ML410 boards do not support the repeated start option. The ML403 OPB IIC is configured as a master and the Aardvark Adapter IIC is configured as a IIC slave. The OPB IIC writes the data to the Aardvark IIC in multiple transactions with the repeated start option enabled. The external IIC device slave address is a 7 bit address defined by SLAVE\_ADDRESS. The number of bytes sent and received is defined by SEND\_COUNT and RECEIVE\_COUNT.

Figure 17 shows the repeated start example.

Specify 0x70 as the Address. The SPI Control is not used. The transaction log shows 16 write and 16 read transactions at address 70.

| lex: ente.<br>Rx Bytes:<br>number o<br>Savi | of bytes | "                                              | s Set                                          | Enable<br>Disab                                                                                                                                               | ed le                                                                                                                                                         | SPI CC<br>Polarity:<br>© Railing/F<br>Falling/F<br>Master   SI <sub>4</sub><br>SS Polarity:<br>MOSI Messa                                                                                                                                        | alling<br>Rising<br>ave  <br>(• SS Active                                                                                                                                                                                                                 | Phase:<br>© Sample/<br>© Setup/S<br>© Low © SS A                                                                                                                                                                                                                                                                                                            | 'Setup<br>ample                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t 4000 V kł<br>Order:<br>MSB<br>LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------|----------|------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rx Bytes:<br>number (                       | of bytes | Í                                              |                                                | Disab                                                                                                                                                         | e<br>le                                                                                                                                                       | <ul> <li>Rising/F</li> <li>Falling/F</li> <li>Master SIa</li> <li>SS Polarity:</li> </ul>                                                                                                                                                        | Rising<br>ave  <br>I SS Active                                                                                                                                                                                                                            | <ul> <li>Sample/</li> <li>Setup/S</li> </ul>                                                                                                                                                                                                                                                                                                                | ample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MSB<br>LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Rx Bytes:<br>number (                       | of bytes | Í                                              |                                                | Disab                                                                                                                                                         | e<br>le                                                                                                                                                       | <ul> <li>Rising/F</li> <li>Falling/F</li> <li>Master SIa</li> <li>SS Polarity:</li> </ul>                                                                                                                                                        | Rising<br>ave  <br>I SS Active                                                                                                                                                                                                                            | C Setup/S                                                                                                                                                                                                                                                                                                                                                   | ample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rx Bytes:<br>number (                       | of bytes | Í                                              |                                                | Disab                                                                                                                                                         | le                                                                                                                                                            | Master Sla<br>SS Polarity:                                                                                                                                                                                                                       | eve  <br>SS Active                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rx Bytes:<br>number (                       | of bytes | Í                                              |                                                |                                                                                                                                                               |                                                                                                                                                               | SS Polarity:                                                                                                                                                                                                                                     | • SS Active                                                                                                                                                                                                                                               | e Low C SS A                                                                                                                                                                                                                                                                                                                                                | active Hij                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gh                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| number (                                    | of bytes | s)                                             |                                                | Set Re                                                                                                                                                        |                                                                                                                                                               | SS Polarity:                                                                                                                                                                                                                                     | • SS Active                                                                                                                                                                                                                                               | ELOW C SS A                                                                                                                                                                                                                                                                                                                                                 | uctive Hij                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | gh                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                             |          | s)                                             | 2                                              | Set Re                                                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                             |          |                                                | 8                                              | Set Re                                                                                                                                                        |                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ć                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Savi                                        | 1        |                                                | ×                                              | Set Re                                                                                                                                                        | sp.                                                                                                                                                           |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Savi                                        | 1        |                                                |                                                | Serne                                                                                                                                                         | <u>эр.</u>                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Savi                                        | 1        |                                                | X                                              |                                                                                                                                                               |                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Savi                                        | 1        |                                                | ×                                              |                                                                                                                                                               |                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

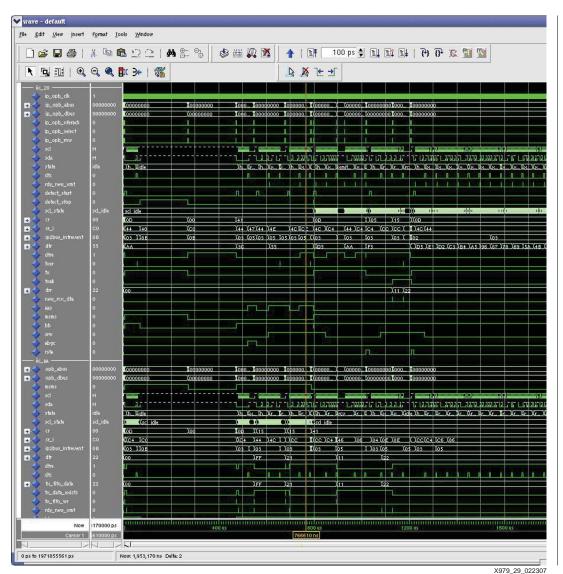

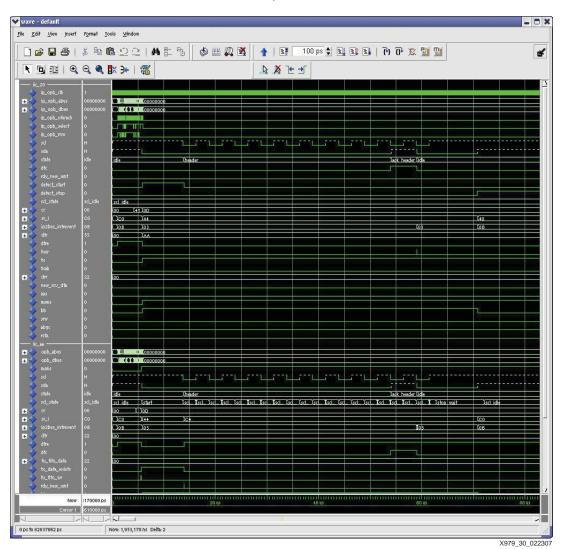

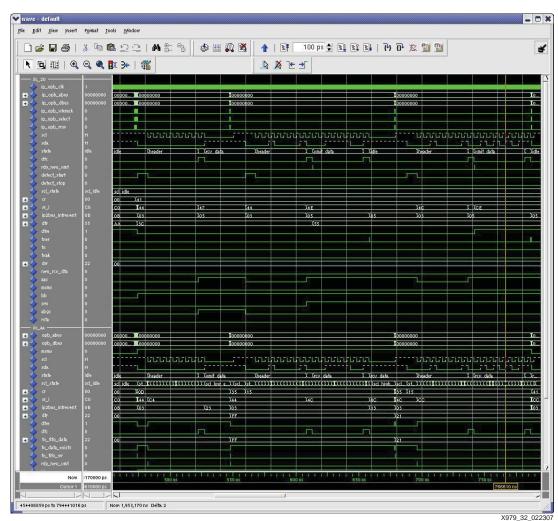

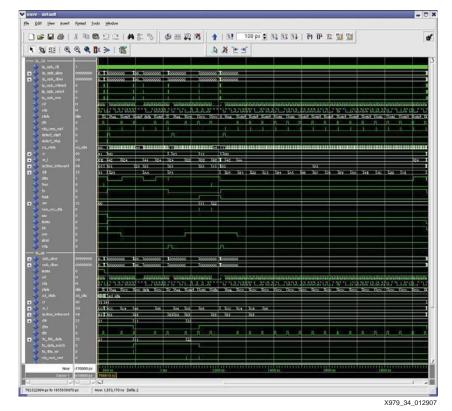

| Savi                                        | 1        |                                                |                                                |                                                                                                                                                               |                                                                                                                                                               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |